CPU Store Buffer #

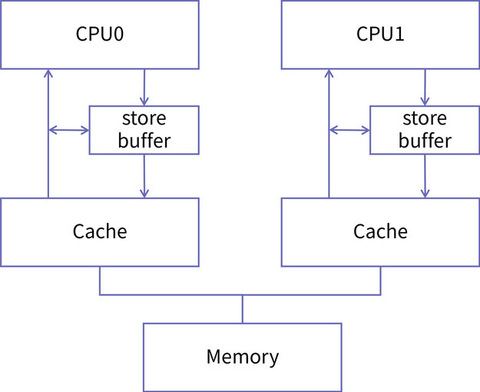

CPU 的设计者为每个核都添加了一个名为 store buffer 的结构,store buffer 是硬件实现的缓冲区,它的读写速度比缓存的速度更快,所有面向缓存的写操作都会先经过 store buffer。

store buffer会收集多次写操作,然后在合适的时机进行提交。增加了 store

buffer 以后的 CPU 缓存结构是这样的:

在这样的结构里,如果 CPU 的某个核再要对一个变量进行赋值,它就不必等到所有的同伴都确认完,而是直接把新的值放入 store buffer,然后再由 store

buffer 慢慢地去做核间同步,并且将新的值刷入到 cache 中去就好了。而且,每个核的 store buffer 都是私有的,其他核不可见。

在这样的结构里,如果 CPU 的某个核再要对一个变量进行赋值,它就不必等到所有的同伴都确认完,而是直接把新的值放入 store buffer,然后再由 store

buffer 慢慢地去做核间同步,并且将新的值刷入到 cache 中去就好了。而且,每个核的 store buffer 都是私有的,其他核不可见。

我们现在来举个例子。我们使用两个 CPU,分别叫做 CPU0 和 CPU1,其中 CPU0 负责写数据,而 CPU1 负责读数据,我们看看在增加了 store buffer 这个结构以后,它们在进行核间同步时会遇到什么问题。

假如 CPU0 刚刚更新了变量 a 的值,并且将它放到了 store buffer 中,CPU0 自己接着又要读取 a 的值,此时,它会在自己的 store buffer 中读到正确的值。

那如果在这一次修改的 a 值被写入 cache 之前,CPU0 又一次对 a 值进行了修改呢?那也没问题,这次更新就可以直接写入 store buffer。因为 store buffer 是 CPU0 私有的,修改它不涉及任何核间同步和缓存一致性问题,所以效率也得到了比较大的提升。