D锁存器 #

为了让存储电路可以保持记忆的能力,我们可以考虑为这种电路引入保持位,当保持位为 1 时,数据可以被存储进电路,当存储完成以后,保持位变为 0,输入就不能再影响输出了。

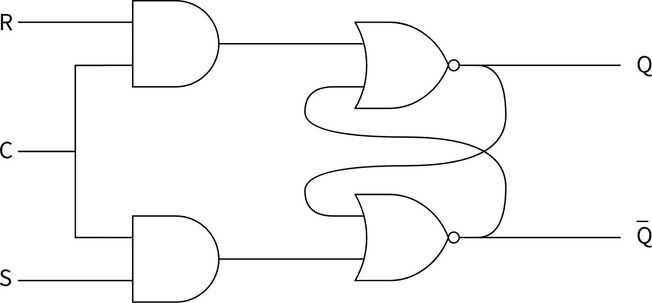

如下图所示,通过增加两个与门来实现保持位 C。当保持位为 1 时,RS 锁存器的功能与不加保持位时完全相同,当保持位为 0 时,则 R 端和 S 端不论取什么值,都不再起作用了。

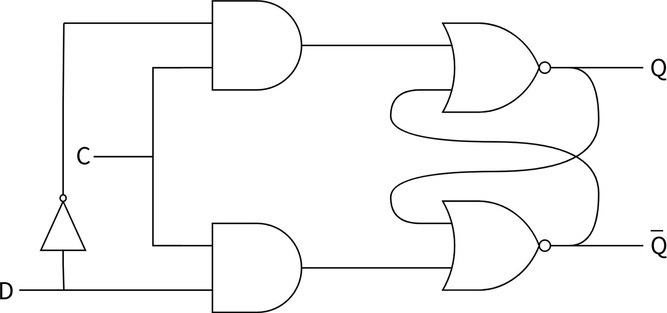

我们再对上图进行更深一步的分析,R 和 S 同时为 0 的情况,可以使用保持位为 0 来代替。R 和 S 同时为 1 的情况是非法情况,所以我们可以使用一个非门,把 R 和 S 合并成一个信号 D,这样的话,电路的输入端就可以进一步化简,如下图所示:

上面电路的保持位为 1 时,输出 Q 可以反应输入 D 的变化,当保持位为 0 时,输出 Q 保持原来的值不变。这种电路被称为电平触发的 D 型锁存器。其中的 D 代表数据 Data。

我们知道信号在传输的过程中容易产生毛刺等不稳定的现象,所以在保持位为 1 的期间,如果输入信号还是不能稳定的话,那么输出将随着输入的改变而发生相应的变化。这种情况下,锁存器的状态就难以稳定。我们把在保持位为 1 期间,锁存器发生多次翻转的情况称为空翻。

在实际应用中,人们还是希望存储电路有良好的稳定性,从这个角度上看,电平触发的锁存器的抗干扰能力相对较差。